低電圧で動作するCMOSリファレンス電圧回路

Low Voltage Operation CMOS Voltage Reference Circuit

大石 秀伸

*大仁 正則

*渡辺 博文

**Hidenobu OHISHI Masanori DAININ Hirobumi WATANABE

要 旨

_________________________________________________

本論文は,不純物およびゲート長Lの異なるゲート電極を持った,2つのCMOSトランジス タで構成されたリファレンス電圧(以下,Vref)回路にて,バックバイアス効果を利用した 新しいLow Voltage Vref回路が,既に実用化されているConventional Vref回路と比べて,低電 圧で動作可能であること,ウェハ面内ばらつきが良好なこと,温度特性が良好なこと,消費 電流が小さくなることを示した.

ABSTRACT _________________________________________________

This paper presents the low voltage operation CMOS reference circuit consisting of a pair of transistors, which have different types of impurities and unmatched lengths of poly Si gates. The measured results for the low voltage reference revealed that the voltage reference has a lower voltage operation, good output voltage reproducibility, lower temperature coefficient, and lower current consumption.

* 電子デバイス事業部 生産室

Production Department, Electronic Devices Divison ** リコー技術研究所

1.

はじめに

電源ICなどのアナログ電子回路では,精度の高い 制御や低消費電力化が必要となっている.高精度化 に特に重要となる回路の1つに,リファレンス電圧 (以下,Vref)回路がある.我々はこれまでVref回 路の高精度化の開発を行ってきた1). また近年,リコーが市場で大きなシェアを持つリ チウムイオン電池保護ICにおいて,検出電圧を低電 圧化して検出回路を低消費電流化することが電池の 長時間使用に貢献するため,低電圧化技術も重要に なってきており,キー回路となるVref回路の低電圧 化のニーズが高まっている. Vref回路は,①バンドギャップリファレンス回 路2,3),②チャンネル不純物濃度を変えて閾値電圧 (以下,Vth)の差を利用した回路4),③ゲート仕事 関数差を用いた回路が主に使用されているが5),こ れらのVref回路は,電源電圧を1V以下に下げること が で き ない ( ①お よ び③) , 温 度特 性 が大 きい (②),というように,今後の低電圧化にあたって は,いずれも課題を抱えている. 我々は先に,一般的なCMOSプロセスを用いなが ら,回路設計を工夫して,0.55 Vという低電圧で動 作するLow Voltage Vref回路を実現した6).このVref回路は,ウェハ面内ばらつきが小さく,安定した温 度特性を持ち,消費電流が小さいこともわかった. 本論文では,この低電圧で動作するLow Voltage Vref回路にて,ウェハ面内ばらつき,温度特性,消 費電流を従来型のConventional Vref回路と比較し, 性能の有意性について論じる.

2.

理論

2-1

仕事関数差Vrefの理論

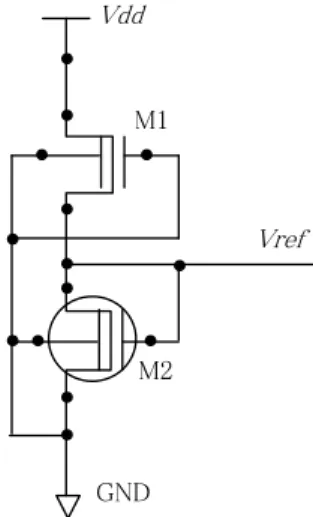

これまでにリコーで開発されてきたVref回路のう ち,代表的なものとして,ゲート仕事関数差を用い たVref回路がある.この回路は,チャンネルの不純 物濃度は同じで,ポリSiゲート電極の極性が異なる 2つのNチャンネル型CMOSトランジスタM1, M2で 構成されている (Fig. 1).ゲート酸化膜容量Cox, ゲート電極の長さL,ゲート電極の幅W等のパラ メータはM1とM2で共通であるが,M1には高濃度N 型ゲート電極,M2には高濃度P型ゲート電極を使用 している.そのためVrefは(1)式のように,ゲート電 極の仕事関数φgateの差で表される. (1) ここで,VthM1はM1の閾値電圧,VthM2はM2の閾 値電圧,kはボルツマン定数,Tは温度,qは電荷, Niは真性半導体のキャリア濃度,Np+は高濃度P型 ゲート電極を使用したトランジスタM2のキャリア 濃度,Nn+は高濃度N型ゲート電極を使用したトラ ンジスタM1のキャリア濃度である. (1)式で示されるVrefは,正の温度特性を持つ.2-2

Conventional Vref回路

この温度特性を低減させるために,2つのトラン ジスタM1, M2のゲート電極の長さLをそれぞれ固有 の 値 とし た回 路 (Conventional Vref回路)がある (回路図はFig. 1と同じ).このVref回路では,仕 事関数差で発生する温度特性を,L長が異なるため に発生する移動度μ(特にフォノン散乱に関わるμPH) の温度特性の差で補正することができるため,さら に温度特性の良いVrefを実現できる.(

)

2 i n p i n i p n p M1 2 M N N N ln q kT N N ln q kT -N N ln q kT gate -gate Vth -Vth Vref + + + + + + = = = = ・ ・ ・ ・ φ φFig. 1 (Conventional) Vref circuit. ここで,フォノン散乱に関わる移動度μPHは,以 下の(2)式で表されるように,L長に依存する電界効 果移動度Eeffが温度特性に影響を与えることがわか る7). (2)

Fig. 1のConventional Vref回路において,M1とM2 には同じドレイン電流Idが流れるので,(3)式の関係 が成り立つ. (3) Conventional Vref回路では,Vref = VgsM2であるこ とから,(3)式を変形すると,以下の(4)式が成り立 つ. (4)

Fig. 2 Low Voltage Vref circuit.

ここで,VgsM1 = 0Vであり,ゲート酸化膜容量

Cox,ゲート幅Wは2つのトランジスタ間で同じであ

るため,CoxM1 = CoxM2およびWM1 = WM2となる.こ れらを(4)式に代入すると,(5)式が導かれる.

(5)

2-3

Low Voltage Vref回路

従来の方法では,Vrefの温度特性は向上するもの の,電源電圧を1Vよりも下げることは難しかった. そこで電源電圧をさらに引き下げるために,2つの トランジスタを組み合わせたVref回路を工夫した. 従来はM1のソースに接続していたM1のゲートを, Fig. 2に示すように,グラウンドに接続すると, バックバイアス効果によって,ドレイン電流を減ら すことができる.その結果,M1とM2の動作点の電 圧が下がるため,最小動作電圧も下げられることに なる.

Low Voltage Vref回路では,VgsM1 = -Vrefとなるの

で,CoxM1 = CoxM2, WM1 = WM2と合わせて(4)式に代入 すると,Vrefは以下の(6)式で表される. Vdd Vref M1 M2 GND Vdd Vref M1 M2 GND

(

)

(

)

MUEPH0 eff MUETMP uephonon PH T/TNOM E M phonon μ・

=(

)

(

Vgs -Vth)

0 L W μ Cox 2 1 -Vth -gs V L W μ Cox 2 1 Id -Id 2 2 M 2 M M2 M2 2 M 2 M 2 1 M 1 M M1 M1 1 M 1 M 2 M 1 M = = ・ ・ ・ ・(

M1 M1)

2 M 1 M 2 M 2 M 1 M 2 M 1 M 1 M 2 M 2 M Vgs -Vth W L μ Cox W L μ Cox -Vth Vgs Vref ・ ・ ・ ・ ・ ・ ・ = = M1 M2 M1 M2 M1 M2 M1 2 M L μ Vth L μ -Vth L μ Vref・

・

・

・

・

= M1 M2 M1 M2 M1 2 M L μ L μ Vth L μ -Vth L μ Vref・

・

・

・

・

・

+ =3.

実験

8 インチウェハの面内のConventional Vref回路お よびLow Voltage Vref回路の特性ばらつきが測定で きるパターンを設計し,一般的なハーフミクロン CMOSプロセスを用いてウェハを試作した.それぞ れのVref回路は,ウェハ面内268箇所に均等に配置 されており,ウェハ面内ばらつきの評価には全点の 測定結果を用いた.また,2つのトランジスタM1, M2のL長の比 (Lratio = LM1/LM2) を0.25~0.75まで変 えたVref回路を用意した.評価として,Vref回路の Vdd - Vref特性,Vrefばらつき,温度特性,消費電流 の比較を行った.

4.

実験結果と考察

4-1

Vdd - Vref特性

Conventional Vref回路とLow Voltage Vref回路のそ れぞれの動作電圧VddとVrefとの関係をFig. 3に示す. バックバイアス効果を利用したLow Voltage Vref回 路 で は , 最 小 動 作 電 圧 が0.8 V と な っ た . Conventional Vref回路の最小動作電圧2.0 Vに比べ, 0.40倍に低電圧化できた.ここで,最小動作電圧と は,Vdd = 5VのときのVrefに対し,95%のVrefとなる Vddの値である. Fig. 3 Vref vs Vdd.

今回のLow Voltage Vref回路の最小動作電圧0.8 V は,以前の報告6)の最小動作電圧0.55 Vと比較して 高くなっているが,これは,前回のCMOSプロセス テクノロジーがサブハーフミクロン世代で,今回は ハーフミクロン世代という違いがあり,そのために 2つのトランジスタのVthの値が異なることによる. また,Vrefについても,Conventional Vref回路が

1.4 Vであるのに対し,Low Voltage Vref回路では 0.5 Vと,0.36倍に下げることができる.Vrefの低下 については,(6)式のVthM1がバックバイアス効果に より上昇したことによる. 今回の測定には,いずれもLratio = 0.5のVref回路 を使用しているので,2 LM1 = LM2である.また,M1 とM2はフォノン散乱の移動度の項が異なるものの, チャンネルの不純物濃度は同じなので,μM1 = μM2と する.これらをConventional Vref回路の(5)式に代入 すると,以下の(7)式のようになる. (7)

Low Voltage Vref回路の(6)式に代入すると,以下 の(8)式のようになる.

(8)

Vrefが出力されている動作点でのVthをそれぞれ

(7)式および(8)式に代入すると,Conventional Vref 回路,Low Voltage Vref回路のVrefはそれぞれ1.26 V, 0.46 Vとなり,実測値とおよそ一致する.

4-2

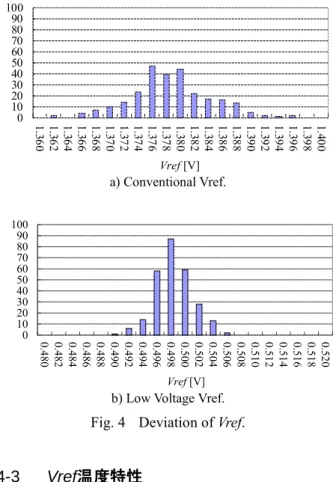

Vrefばらつき

Conventional Vref回路およびLow Voltage Vref回路 の面内268箇所のVref測定結果を Table 1に示す.こ こでは,標準偏差σでの比較を行っている.また, それぞれのヒストグラムを,Fig. 4 a)およびb)に示す. これより,Low Voltage Vref回路では,Conventional Vref回路に比べVrefのσが小さくなっていることがわ かる. 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 0 1 2 3 4 5 Vref [V ] Vdd [V] Conventional Low Voltage 1 M 2 M - 2 Vth Vth Vref = ・

(

1 1 2)(

VthM2- 2 VthM1)

Vref ・ ・ + =以下,Low Voltage Vref回路の方が,σが小さく なっている理由について,(5)式および(6)式から考 察する. Vref回路では,L = 10 μm以上の十分大きいL長を 使用しているため,LM1, LM2は,σへの影響は十分小 さい.今回の測定結果から,トランジスタの移動度 μのばらつきは,Vthのばらつきの1/4程度であり, Vrefのばらつきに支配的なのはVthM1, VthM2であるこ とがわかった.

Low Vloltage Vref の 各 Vth に か か る 係 数 は , Conventional Vrefと比較すると,分母に μ ・M1 LM2 が追加されているので,係数全体の絶対値は小さく なる.以上の理由で,各Vthのσが同等であっても, Low Voltage Vref回路の方が,Vrefのσは小さくなる.

σが小さくなることは,リチウムイオン電池保護 ICの場合,検出電圧の微調整を行うトリミング工程 において有利である.Vref回路を使用して狙いの検 出電圧を得るには,Vref回路に接続した抵抗の比を 変えることで,狙いの検出電圧に変換しているが, Vrefに応じてトリミング工程にて抵抗につながる配 線をレーザーで切断し,抵抗の比を微調整すること で,製造工程で発生するVrefのばらつきを打ち消す ことができる.しかし,抵抗体自体にもばらつきが あるので,Vrefのσを小さくできれば,微調整に用 いる抵抗体の本数を削減することができるため,検 出電圧のばらつき低減,およびチップの小型化に有 利である.

Table 1 Comparison of Deviation of Vref.

Conventional Low Voltage AVE (V) 1.3776 0.4974 MAX (V) 1.3947 0.5044 MIN (V) 1.3608 0.4892 σ (V) 0.0057 0.0026

a) Conventional Vref.

b) Low Voltage Vref.

Fig. 4 Deviation of Vref.

4-3

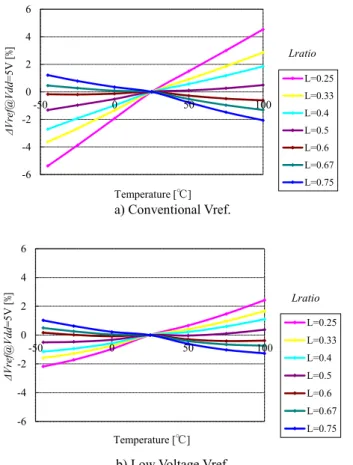

Vref温度特性

Vrefの温度特性は,2つのトランジスタのLratioに

依 存 す る た め ,Conventional Vref回 路お よび Low Voltage Vref回路それぞれについて,各Lratioでの温 度と,25℃のVrefからの変動率との関係について評 価した.測定温度Taでの変動率 (ΔVref %) は,以下 の(9)式で表される. (9) 0 10 20 30 40 50 60 70 80 90 100 1.3 60 1.362 1.364 1.366 1.368 1.370 1.372 1.374 1.376 1.378 801.3 1.382 1.384 1.386 1.388 901.3 1.392 1.394 1.396 1.398 1.400 Vref [V] 0 10 20 30 40 50 60 70 80 90 100 0. 480 0.482 0.484 0.486 0.488 0.490 0.492 0.494 0.496 0.498 5000. 0.502 0.504 0.506 0.508 5100. 0.512 0.514 0.516 0.518 0.520 Vref [V]

( )

( )

(

)

(

)

100 25 T Vref 25 T Vref -Ta Vref % Vref Δ = ×a) Conventional Vref.

b) Low Voltage Vref.

Fig. 5 ΔVref vs Temperature.

結果をFig. 5 a)およびb)に示す.また,Lratioと温 度係数TC (ppm/℃) との関係をFig. 6に示す.これよ り,Conventional Vref回路とLow Voltage Vref回路で は温度係数TC = 0 ppm/℃となるLratioが異なってい ることがわかる.Conventional Vref回路およびLow Voltage Vref回路のLratioを,それぞれ0.57, 0.51に設 定すれば,TC = 0 ppm/℃の安定な温度特性を得るこ とができる. 温度特性のLratio依存性(Fig. 6の傾き)は,Low Voltage Vref回路の方が,Conventional Vref回路より も小さい.これは,バックバイアスにより電界効果 移動度Eeff が小さくなり,結果としてμPH の変動が 小さくなって,Vrefの温度特性も小さくなるためで ある.

Fig. 6 TC vs Lratio.

Fig. 7 Consumption current.

4-4

消費電流

Conventional Vref回路およびLow Voltage Vref回路 それぞれについて,Lratio = 0.5のときの消費電流の 比較を行った.結果をFig. 7に示す.これより, Low Voltage Vref回路では,Conventional Vref回路に 比べ消費電流が0.14倍に抑えられていることがわか る.Low Voltage Vref回路の25℃での消費電流は, 1.7 μAであった. -6 -4 -2 0 2 4 6 -50 0 50 100 ΔVref @ Vdd =5V [ %] Temperature [℃] L=0.25 L=0.33 L=0.4 L=0.5 L=0.6 L=0.67 L=0.75 Lratio -6 -4 -2 0 2 4 6 -50 0 50 100 ΔVref@ Vdd =5V [% ] Temperature [℃] L=0.25 L=0.33 L=0.4 L=0.5 L=0.6 L=0.67 L=0.75 Lratio y = -855.6ln(x) - 487.05 y = -494.7ln(x) - 332.87 -1000 -800 -600 -400 -200 0 200 400 600 800 1000 0.0 0.5 1.0 1.5 TC [ppm /℃ ] Lratio Conventional Low Voltage 0 2 4 6 8 10 12 14 -50 0 50 100 Temperature [℃] Id d @ V dd = 5 V [µ A ] Conventional Low Voltage 対数 (Conventional) 対数 (Low Voltage)

5.

結論

仕事関数の異なる2種類のポリSiゲートを用いた Vref回路にて,一般的なCMOS製造プロセスを変え ることなく,一方のゲートをグラウンドに接続する だけで,最小動作電圧を0.40倍,Vrefを0.36倍に低 下できることがわかった.また,消費電流を0.14倍 に小さくできるということもわかった.面内ばらつ きや温度特性についても良好な特性が得られた. Low Voltage Vref回路は,今後の電源ICにおいて, 低電圧化のコア技術となる.参考文献 _________________________________ 1) H. Watanabe et al.: CMOS Voltage Reference Based on Gate Work Function Differences in Poly-Si Controlled by Conductivity Type and Impurity Concentration, IEEE J. Solid-State Circuits, Vol. 38, No. 6, pp. 987-994 (2003).

2) Ming-Dou Ker et al.: New curvature-compensation technique for CMOS bandgap reference with sub-1-V operation, IEEE International Symposium on

ISCAS, Vol. 4, pp. 3861-3864 (2005).

3) Y. Okuda et al.: A Trimming-Free CMOS Bandgap-Reference Circuit with Sub-1-V-Supply Voltage Operation, Symp. VLSI Circuits, pp. 96-97 (2007). 4) Guiseppe De Vita et al.: A Sub-1V, 10 ppm/°C,

Nanopower Voltage Reference Generator, 32nd

European Solid-State Circuits Conference, pp.

307-310 (2006).

5) H. J. Oguey et al.: MOS voltage reference based on polysilicon gate work function difference, IEEE J.

Solid-State Circuits, Vol. SC-15, No. 3, pp. 264-269

(1980).

6) H. Watanabe et al.: 0.55V Operation CMOS Voltage Reference based on the Work Function Difference of Poly Si Gates, IMFEDK2010, pp. 42-43 (2010). 7) Hiroshima University & STARC: HiSIM HV 1.2.0